For timing-critical applications such as video, pure hardware solutions can enhance the operational capabilities of Xilinx FPGAs.

In many new applications, such as video processing, minimizing FPGA reconfiguration time is critical to avoid losing too many images. Partial reconfiguration refers to the technique of reconfiguring a small portion of a FPGA without affecting the peripheral logic of the FPGA. If you want the human eye to not see the flicker of the image, the reconfiguration can take no more than 40 milliseconds. Except for the smallest FPGA, this time is too short for reconfiguring the entire device. However, in some specific cases, this reconfiguration time needs further compression. Partial reconfiguration techniques have emerged because the partially reconfigured bitstream is smaller than the fully reconfigured bitstream, so reconfiguration takes less time.

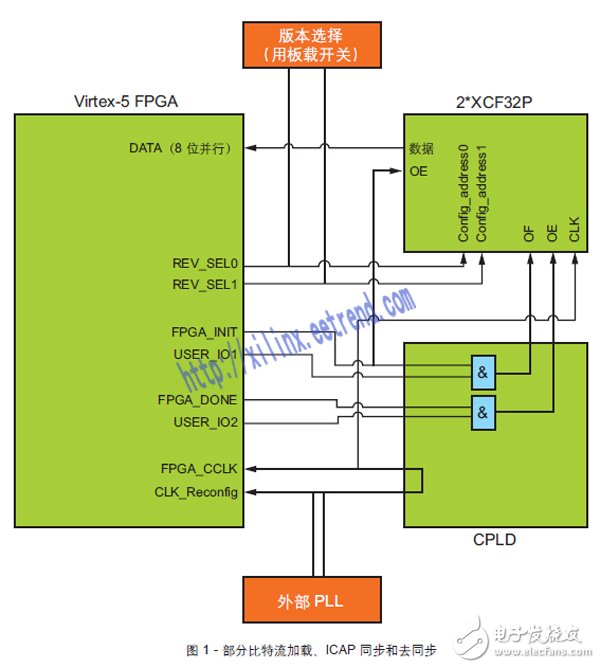

Our developers at Sagem DS have devised a technology that allows FPGA designers to do partial reconfiguration at an extremely fast rate. We use the Xilinx ML507[1] development board to test, verify, and measure timing. In general, the board consists of a Virtex®-5 FPGA (XC5VFX70T-FFG1136), a CPLD (used as a routing component), and two XCF32P memories (Xilinx platform flash).

MICROBLAZE vs. Hardware Solutions In many technical documents, partial reconfiguration (PR) technology uses an internal controller such as MicroBlaze® or an external processor. Depending on the configuration, implementing a processor within an FPGA requires development time and consumes a large amount of device resources. Also, using an external processor increases the cost and takes up board space. In addition, there is a delay in the bus like PLB or AXI, which will lengthen the reconfiguration time.

For all of these reasons, we have adopted a pure hardware solution based on a small state machine and loaded the bitstream using the Internal Configuration Access Port (ICAP) interface. This approach has several advantages: there is no latency, this approach is essentially resource-intensive (less than 300 lookup tables are used on the FPGA), and designers can optimize the timing of partial reconfiguration.

Development Process Overview From VHDL concepts to the creation of bitstreams and partial bitstreams, except for the absence of an embedded processor, our pure hardware partial reconfiguration process is outlined in the Xilinx Tutorial, User Guide [2] and Application Guide. The same process. Users must define reconfigurable zones (RPs) in PlanAheadTM and import reconfigurable modules (RMs) for each zone. For all configuraTIonruns static logic can be imported from the previously run runs.

During partial reconfiguration, the FPGA must be in slave mode. That is to say, the only available interfaces are JTAG, Slave, Slave SelectMap or ICAP. Completing the reconfiguration requires an external component to drive the CCLK of the FPGA; ICAP is not accessible when the FPGA is first booted. To save time in reconfiguration, you can not use the serial interface. This leaves us with at least two interfaces to choose from: SelectMap and ICAP.

The first option is to use the SelectMap interface for all and part of the bitstream to load. This configuration method requires a Bitgen option (-g Persist) to be added when creating the bitstream. This allows the FPGA to maintain control of the SelectMap pin to load a portion of the bitstream. Also in the case of SelectMap, no signal is very accurate to indicate the end of the process (such as a fully configured DONE signal). So it is difficult to know exactly when the partial reconfiguration ends. The user must create a module that estimates when all configuration data has been sent.

That's why we ended up choosing to load part of the bitstream using ICAP primitives. ICAP is not a self-configuring interface like SelectMap, so after we use SelectMap to implement the FPGA's first boot, the ICAP primitives are fully controlled by the user code.

Compared to a pure SelectMap design, ICAP has two major advantages. First, the transformation (SelectMap is used for the first time, ICAP for partial bitstream loading) is transparent to the user and does not require the Bitgen option. Therefore the user can control the memory pins. Second, and the main advantage, ICAP can continuously reflect the status to the output. This state changes if the FPGA is in reconfiguration mode. This allows the user to "see" the end of the partial reconfiguration.

Reconfiguration features and components In our company, we use FPGAs to develop video processing applications. These features use logic components, some BRAM components, and a large number of DSPs. It is very meaningful to study the reconfiguration time of these three components, because it can guide us to set the size of the reconfigurable area based on the answer to the following two questions: 40 millisecond image refresh time to meet our application requirements, we How should I set the size of the reconfigurable area? How many different components do we need to put in this area? We answered these two questions by testing different types of configurations on the ML507.

As shown in Figure 1, on the ML507 we chose an external phase-locked loop (PLL) as the reference clock for partial reconfiguration control. Part of the connection is not what we deliberately choose, but the board design needs. The schematic does not show a protection circuit that avoids line level conflicts in the trace. The clock frequency is 33MHz, which is the highest rate of two XCF32P memories on the development board. [3] The data bus is 8 bits wide and can achieve data transfer rates of up to 264Mbps.

A TPU Screen Protector made of the super toughness of the honeycomb structure. Its unique ultra-soft properties allow it to cover the most complex curves and contours in a device.

The self-healing design of the Hydrogel Screen Protector can protect the display screen of the device from damage, leave no air bubbles, and maintain the sensitivity of the touch screen. Advanced anti-fingerprint and dust- and oleophobic overlays keep your screen smudge- and dirt-free. This overlay is also important in providing maximum touch sensitivity for improved high-speed glide and optimal touch response.

The optical transparency of the Hydrogel Film is more than 90%, showing you the most original screen color and bringing the most realistic visual experience.

If you want to know more about the product information of the Hydrogel Screen Protector for Huawei, please click the product details to view the parameters, model, picture, price and other information of the Huawei Screen Protector.

Whether you are a group or an individual, we will do our best to provide you with accurate and comprehensive information about Hydrogel Screen Protectors!

Screen Protector For Huawei,Hydrogel Film for Huawei,TPU Screen Protector for Huawei,Hydrogel Screen Protector for Huawei

Shenzhen Jianjiantong Technology Co., Ltd. , https://www.jjtscreenprotector.com